Cadence入门05:绘制原理图

1、基本操作:

1、 Place Part(P):放置元件

2、 Place wire(W):连接相连的pin脚

3、 Place Auto wire:自动连线

4、 Place bus(B):总线连接

5、 Place junction(J):交叉点连接,两条wire相交有两种连接关系:连或不连,加J为连

6、 Place bus entry(E):可以理解为总线入口,有bus必有entry

7、 Place net alias(N):相当于wire,用于连接距离远的Pin脚,仅限于同一page电气连接

8、 Place power(F):放置电源

9、 Place ground(G):放置地

10、 Place off-page connector:类似alias,但alias仅用于同一页面,而off-page用于不同页面之间的电气连接

11、 Place no connect(X):用于无电气连接的pin脚,不放会报错

12、 Place text(T):放置文本

2、常用操作:

1、按住Ctrl滚动鼠标滚轮放大缩小原理图(以鼠标指针为中心);直接滚动鼠标滚轮上下移动;按住Shift滚动左右移动

2、改变原理图尺寸大小:options->Schematic Page Properties->Page Size

3、旋转器件:放置器件前直接按R可旋转,放置后选中按R旋转

4、选中单个或者多个器件,按住Ctrl+鼠标左键,拖动鼠标,可复制所选器件

5、 连线时改变连线角度需先按shift键

6、元件镜像:选定后V键(垂直)和H键(水平)

7、鼠标右键选End mode结束当前操作

8、连线时,终点如不是管脚,双击结束

9、管脚之间不要直接相连,通过线连接以防出错(软件设置管脚之间不允许连接的方法:

Options/Preferences->Miscellaneous->Wire Drag打钩去掉)

3、后期处理:

1、 浏览原理图:选中 .dsn , edit->browse

可以浏览parts、nets等,主要检查是否有漏掉的信息,双击可以打开原理图并高亮显示所选内容

2、 元件替换和更新:右键需要修改的元件,选择Replace cache或Update Cache

Replace cache:用于替换

Update Cache:用于更新

4、 Cleanup Cache:右键Design Cache选择Cleanup Cache用于检测Design Cache与原理图是否一致,并删除多余的内容

4、 移动:默认连线与移动元件一同移动,按住Alt 移动仅元件移动

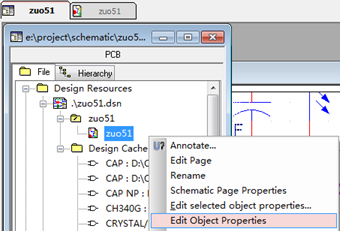

5、 自动编号:右键.dsn 选Annotate 。首先选择Reset part references to ?进行复位,然后选择Unconditional reference update进行编号。

4、 添加footprint(保证与器件封装名称一致):

a、双击元件,找到PCB footprint,右键选择Edit,添加封装名称即可(右键选择Pivot可以切换显示方式)

b、按住Ctrl选择多个元件,右键选择Edit Properties进行添加

c、常用元件可通过元件库添加PCB封装

d、批量添加:右键Page 选择edit Object Properties

5、点击Pivot可以改变视图模式,可多选统一编辑,如下:

6、DRC检查:Tools->Design Rules Check

6、生成netlist:Tools->Create Nelist ,选择PCB Editor确认

7、生成BOM:Reports->CIS Bill of Materials

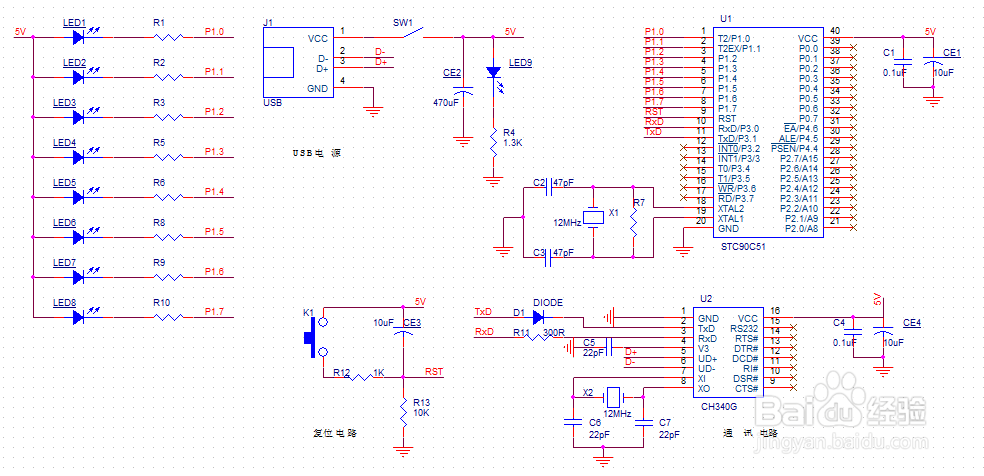

1、原理图实例

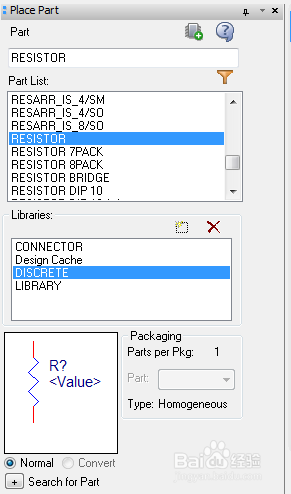

2、放置元件

除J1、U1、U2外,全部使用软件自带封装,在对应封装库进行搜索

如:电阻搜索RES、电容搜索CAP、LED灯搜索LED、开关搜索SW、二极管搜索DIODE、晶振搜索crystal,一般输入元件英文名称即可。

3、电气连接:理论上所有电气连接均可由wire实现,为方便连线实例中加入 net alias

4、后期处理并导出网表netlist(网表用于导入PCB,需保证所有元件均有footprint)