AD中网表的生成与导入

1、第一步,在工程界面下,选择“Design-Netlist For Project-Protel”,导入某个设计工具形成的网表,比如Cadence;

2、第二步,单击鼠标右键,选择“Explore”命令,找到该网表所在的路径;

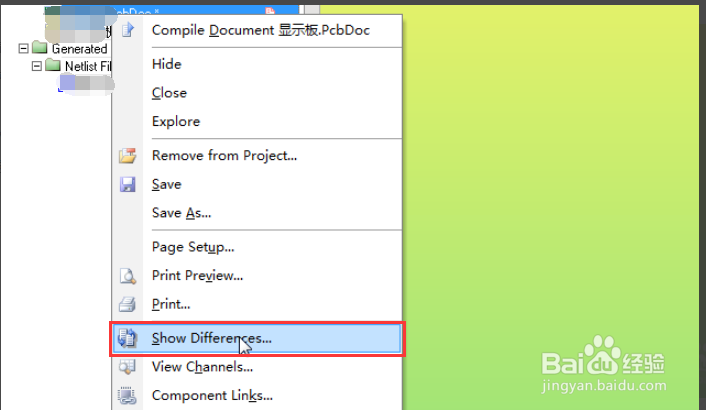

3、第三步,AD导入网表时,选择“Add Existing to Project...”,将网表添加到工程中,选择“Show Differences...”进入网表对比窗口;

4、第四步,勾选“Advanced Mode”。左边是导入的网表,右边需要更新进入的PCB,单击“ok”;

5、第五步,对比结果会出现在窗口中,确定无误后,“Update All in--PCB Document”,把网表和PCB对比的相关所有结果准备导入PCB。

6、第六步,执行“Create Engineering Change Order”命令,进入和直接导入法一样的导入执行窗口,单击“Execute changes”按钮更新进入PCB即可;

1、1.选择“Design-Netlist For Project-Protel”,导入某个设计工具形成的网表,比如Cadence;

2.单击鼠标右键,选择“Explore”命令,找到该网表所在的路径;

3.“Add Existing to Project...”,将网表添加到工程中,选“Show Differences...”进入网表对比窗口;

4.勾选“Advanced Mode”。左边是导入的网表,右边需要更新进入的PCB,对比;

5.对比结果会出现在窗口中,确定无误后导入PCB;

6.执行“Create Engineering Change Order”命令,更新PCB;

声明:本网站引用、摘录或转载内容仅供网站访问者交流或参考,不代表本站立场,如存在版权或非法内容,请联系站长删除,联系邮箱:site.kefu@qq.com。

阅读量:45

阅读量:95

阅读量:92

阅读量:172

阅读量:158